#### SiPHY<sup>™</sup> **OC-192/STM-64 TRANSMITTER**

#### **Features**

Complete SONET/SDH transmitter for OC-192/STM-64 data rates with integrated 16:1 multiplexer and DSPLL<sup>™</sup> based clock multiplier unit:

- Data Rates Supported: OC-192/STM-64, OIF SFI-4 Compliant Interface 10GbE, and 10.7 Gbps FEC

- Low Power Operation 0.6 W (typ)

- Small Footprint: 99-Pin BGA Package (11 x 11 mm)

- DSPLL<sup>™</sup> Based Clock Multiplier Unit w/ selectable loop filter bandwidths

- LVTTL Compatible Outputs

**Reference Sources**

**Output Clock Powerdown**

Operates with 155 or 622 MHz

Optional 3.3 V Supply Pin for

Single 1.8 V Supply Operation

#### Applications

- Sonet/SDH/ATM Routers

- Add/Drop Multiplexers

- **Digital Cross Connects**

- **Optical Transceiver Modules**

- Sonet/SDH Test Equipment

#### Description

The Si5540 is a fully integrated low-power transmitter for high-speed serial communication systems. It combines high speed clock generation with a 16:1 multiplexer to serialize data for OC-192/STM-64 applications. The Si5540 is based on Silicon Laboratories' DSPLL<sup>™</sup> technology which eliminates the external loop filter components required by traditional clock multiplier units. In addition, selectable loop filter bandwidths are provided to ensure superior jitter performance while relaxing the jitter requirements on external clock distribution subsystems. Support for data streams up to 10.7 Gbps is also provided for applications that employ forward error correction (FEC).

The Si5540 represents a new standard in low jitter, low power and small size for 10 Gbps serial transmitters. It operates from a single 1.8 V supply over the industrial temperature range (-40°C to 85°C).

#### REESEL REFCLK REFRATE . TXCI K16IN TXLOL DSPLL™ ÷16 TXCLK16OUT BWSEL сми TXCLKDSBL TXCLKOUT ┥ TXCLK16IN NN E FO 32 5 TXDIN[15:0] TXDOUT 🗲 FIFORST Reset Bias Control FIFOERR REXT RESET TXSQLCH TXMSBSEL

#### **Functional Block Diagram**

# TABLE OF CONTENTS

# Section

# Page

| Electrical Specifications      | 4  |

|--------------------------------|----|

| Functional Description         | 9  |

| DSPLL™ Clock Multiplier Unit 9 | 9  |

| Reference Clock                | 9  |

| Serialization                  | 9  |

| Reset                          | 10 |

| Clock Disable                  | 10 |

| Bias Generation Circuitry      | 10 |

| Differential Output Circuitry  |    |

| Si5540 Pinout: 99-Pin BGA      | 12 |

| Pin Descriptions: Si5540       |    |

| Ordering Guide                 |    |

| Package Outline                | 18 |

| Contact Information            | 20 |

# **Electrical Specifications**

#### **Table 1. Recommended Operating Conditions**

| Parameter                   | Symbol            | Test Condition | Min* | Тур | Max* | Unit |

|-----------------------------|-------------------|----------------|------|-----|------|------|

| Ambient Temperature         | T <sub>A</sub>    |                | -40  | 25  | 85   | °C   |

| LVTTL Output Supply Voltage | V <sub>DD33</sub> |                | 1.71 |     | 3.47 | V    |

| Si5540 Supply Voltage       | V <sub>DD</sub>   |                | 1.71 | 1.8 | 1.89 | V    |

Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

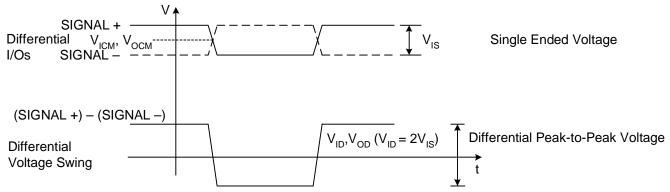

Figure 1. Differential Voltage Measurement (TXDIN, TXDOUT, TXCLK16IN, TXCLK16OUT)

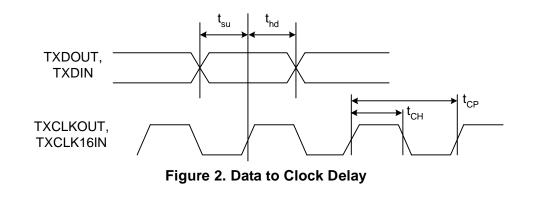

Figure 3. Rise/Fall Time Measurement

# Table 2. DC Characteristics, $V_{DD}$ = 1.8 V ( $V_{DD}$ = 1.8 V ±5%, $T_A$ = -40°C to 85°C)

| Parameter                                                                                               | Symbol           | Test Condition                              | Min   | Тур  | Мах   | Unit          |

|---------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------|-------|------|-------|---------------|

| Supply Current                                                                                          | I <sub>DD</sub>  |                                             | —     | 333  | TBD   | mA            |

| Power Dissipation                                                                                       | PD               |                                             | —     | 0.6  | TBD   | W             |

| Common Mode Output Voltage<br>(TXDOUT,TXCLKOUT)                                                         | V <sub>OCM</sub> |                                             | .8    | 0.9  | 1.0   | V             |

| Differential Output Voltage Swing (TXDOUT,TXCLKOUT), Differential pk-pk                                 | V <sub>OD</sub>  | See Figure 1                                | 800   | 1000 | 1200  | mV<br>(pk-pk) |

| LVPECL Input Voltage High (REFCLK)                                                                      | V <sub>IH</sub>  |                                             | 1.975 | 2.3  | 2.59  | V             |

| LVPECL Input Voltage Low (REFCLK)                                                                       | V <sub>IL</sub>  |                                             | 1.32  | 1.6  | 1.99  | V             |

| LVPECL Input Voltage Swing (REFCLK),<br>Differential pk-pk                                              | V <sub>ID</sub>  |                                             | 250   |      | 2600  | mV<br>(pk-pk) |

| LVPECL Input Common Mode (REFCLK)                                                                       | V <sub>ICM</sub> |                                             | 1.65  | 1.95 | 2.30  | V             |

| Input Impedance<br>(REFCLK, TXDIN, TXCLK16IN)                                                           | R <sub>IN</sub>  | Each input to common mode                   | 42    | 50   | 58    | Ω             |

| LVDS Input High Voltage (TXDIN,<br>TXCLK16IN)                                                           | V <sub>IH</sub>  |                                             | —     |      | 2.4   | V             |

| LVDS Input Low Voltage (TXDIN,<br>TXCLK16IN)                                                            | V <sub>IL</sub>  |                                             | 0.0   |      |       | V             |

| LVDS Input Voltage, Single Ended pk-pk<br>(TXDIN, TXCLK16IN)                                            | V <sub>ISE</sub> |                                             | 100   | _    | 600   | mV<br>(pk-pk) |

| LVDS Input Common Mode Voltage<br>(TXDIN, TXCLK16IN)                                                    | V <sub>ICM</sub> |                                             | .8    | 2.0  | 2.4   | V             |

| LVDS Output High Voltage<br>(TXCLK16OUT)                                                                | V <sub>OH</sub>  | 100 Ω Load<br>Line-to-Line                  | TBD   |      | 1.475 | V             |

| LVDS Output Low Voltage<br>(TXCLK16OUT)                                                                 | V <sub>OL</sub>  | 100 Ω Load<br>Line-to-Line                  | 0.925 |      | TBD   | V             |

| LVDS Output Voltage, Single Ended pk-pk<br>(TXCLK16OUT)                                                 | V <sub>OSE</sub> | 100 Ω Load<br>Line-to-Line, See<br>Figure 1 | 250   | 400  | 550   | mV<br>(pk-pk) |

| LVDS Output Common Mode Voltage<br>(TXCLK16OUT)                                                         | V <sub>OCM</sub> |                                             | 1.125 | 1.20 | 1.275 | V             |

| Output Short to GND<br>(TXCLK16OUT, TXDOUT, TXCLKOUT)                                                   | I <sub>SC-</sub> |                                             |       | 25   | TBD   | mA            |

| Output Short to V <sub>DD</sub><br>(TXCLK16OUT, TXDOUT, TXCLKOUT)                                       | I <sub>SC+</sub> |                                             | TBD   | -100 |       | μA            |

| LVTTL Input Voltage Low<br>(TXCLKDSBL, FIFORST, TXSQLCH,<br>BWSEL, REFRATE, REFSEL, TXMSBSEL,<br>RESET) | V <sub>IL2</sub> |                                             |       |      | 0.8   | V             |

## Table 2. DC Characteristics, $V_{DD}$ = 1.8 V (Continued)

$(V_{DD} = 1.8 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                                                                          | Symbol           | Test Condition | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------------|------------------|----------------|-----|-----|-----|------|

| Input Voltage High<br>(TXCLKDSBL, FIFORST, TXSQLCH,<br>BWSEL, REFRATE, REFSEL, TXMSBSEL,<br>RESET) | V <sub>IH2</sub> |                | 2.0 |     | —   | V    |

| Input Low Current<br>(TXCLKDSBL, FIFORST, TXSQLCH,<br>BWSEL, REFRATE, REFSEL, TXMSBSEL,<br>RESET)  | Ι <sub>ΙL</sub>  |                | _   |     | 10  | μA   |

| Input High Current<br>(TXCLKDSBL, FIFORST, TXSQLCH,<br>BWSEL, REFRATE, REFSEL, TXMSBSEL,<br>RESET) | lιΗ              |                | _   |     | 10  | μA   |

| Input Impedance<br>(TXCLKDSBL, FIFORST, TXSQLCH,<br>BWSEL, REFRATE, REFSEL, TXMSBSEL,<br>RESET)    | R <sub>IN</sub>  |                | 10  |     | _   | kΩ   |

| LVTTL Output Voltage Low                                                                           | V <sub>OL2</sub> | VDD33 = 1.8 V  |     |     | 0.4 | V    |

| (FIFOERR, TXLOL)                                                                                   |                  | VDD33 = 3.3 V  |     |     | 0.4 |      |

| LVTTL Output Voltage High                                                                          | V <sub>OH2</sub> | VDD33 = 1.8 V  | 1.4 | _   |     | V    |

| (FIFOERR, TXLOL)                                                                                   |                  | VDD33 = 3.3 V  | 2.4 |     |     |      |

# Table 3. AC Characteristics (TXCLK16OUT, TXCLK16IN, TXCLKOUT, TXDIN, TXDOUT) $(V_{DD =} 1.8 \text{ V} \pm 5\%, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C})$

| Parameter                              | Symbol                          | Test Condition                  | Min        | Тур  | Мах  | Unit     |

|----------------------------------------|---------------------------------|---------------------------------|------------|------|------|----------|

| TXCLKOUT Frequency                     | f <sub>clkout</sub>             |                                 |            | 9.95 | 10.7 | GHz      |

| TXCLKOUT Duty Cycle                    |                                 | tch/tcp, Figure 2               | 45         | _    | 55   | %        |

| Output Rise Time<br>(TXCLKOUT, TXDOUT) | t <sub>R</sub>                  | Figure 3                        | —          | 25   |      | ps       |

| Output Fall Time<br>(TXCLKOUT, TXDOUT) | t <sub>F</sub>                  | Figure 3                        | _          | 25   |      | ps       |

| TXCLKOUT Setup to TXDOUT               | t <sub>su</sub>                 | Figure 2                        | 25         |      |      | ps       |

| TXCLKOUT Hold From TXDOUT              | t <sub>hd</sub>                 | Figure 2                        | 25         | —    |      | ps       |

| Output Return Loss                     |                                 | 400 kHz–10 GHz<br>10 GHz–16 GHz | TBD<br>TBD | _    |      | dB<br>dB |

| TXCLK16OUT Frequency                   | f <sub>CLKIN</sub>              | Figure 2                        |            | 622  | 667  | MHz      |

| TXCLK16OUT Duty Cycle                  |                                 | tch/tcp, Figure 2               | 40         | —    | 60   | %        |

| TXCLK16OUT Rise & Fall Times           | t <sub>R</sub> , t <sub>F</sub> |                                 | 100        | —    | 300  | ps       |

| TXDIN Setup to TXCLK16IN               | t <sub>DSIN</sub>               |                                 |            | —    | 300  | ps       |

| TXDIN Hold from TXCLK16IN              | t <sub>DHIN</sub>               |                                 | _          | —    | 300  | ps       |

| TXCLK16IN Frequency                    | f <sub>CLKIN</sub>              |                                 |            | 622  | 667  | MHz      |

| TXCLK16IN Duty Cycle                   |                                 | tch/tcp, Figure 2               | 40         | _    | 60   | %        |

| TXCLK16IN Rise & Fall Times            | t <sub>R</sub> , t <sub>F</sub> |                                 | 100        |      | 300  | ps       |

## Table 4. AC Characteristics (Clock Multiplier Characteristics)

$(V_{DD} = 1.8 \text{ V} \pm 5\%, \text{ T}_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C})$

| Parameter                                    | Symbol                | Test Condition       | Min  | Тур   | Мах | Unit              |

|----------------------------------------------|-----------------------|----------------------|------|-------|-----|-------------------|

| Jitter Generation—Deterministic              | J <sub>DET(PP)</sub>  | PRBS-23              | _    | 0.020 | TBD | UI <sub>PP</sub>  |

| Jitter Generation—Random                     | J <sub>GEN(RMS)</sub> |                      | —    | 0.005 | TBD | UI <sub>RMS</sub> |

| Jitter Transfer Bandwidth                    | J <sub>BW</sub>       | BWSEL = 0            |      |       | 12  | kHz               |

|                                              |                       | BWSEL = 1            |      |       | 50  | kHz               |

| Jitter Transfer Peaking                      |                       |                      |      | 0.05  | 0.1 | dB                |

| Acquisition Time                             | T <sub>AQ</sub>       | Valid REFCLK         |      | 15    | 20  | ms                |

| Input Reference Clock Frequency              | RC <sub>FREQ</sub>    | REFRATE = 1          | —    | 622   | 667 | MHz               |

|                                              |                       | REFRATE = 0          |      | 155   | 167 | MHz               |

| Input Reference Clock Duty<br>Cycle          | RC <sub>DUTY</sub>    |                      | 40   |       | 60  | %                 |

| Input Reference Clock Frequency<br>Tolerance | RC <sub>TOL</sub>     |                      | -100 |       | 100 | ppm               |

| Note: Bellcore specifications: GR-137        | 7-CORE, Issu          | ue 5, December 1998. | ·    |       |     |                   |

#### Table 5. Absolute Maximum Ratings

| Parameter                                                                                                                         | Symbol                       | Value                           | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------|------|

| DC Supply Voltage                                                                                                                 | V <sub>DD</sub>              | -0.5 to 3.0                     | V    |

| LVTTL Input Voltage                                                                                                               | V <sub>DD33</sub>            | -0.5 to 3.6                     | V    |

| Differential Input Voltages                                                                                                       | V <sub>DIF</sub>             | –0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Maximum Current any output PIN                                                                                                    |                              | ±50                             | mA   |

| Operating Junction Temperature                                                                                                    | T <sub>JCT</sub>             | -55 to 150                      | °C   |

| Storage Temperature Range                                                                                                         | T <sub>STG</sub>             | -55 to 150                      | °C   |

| Package Temperature<br>(soldering 10 seconds)                                                                                     |                              | 275                             | °C   |

| ESD HBM Tolerance (100 pf, 1.5 k $\Omega$ )                                                                                       |                              | TBD                             | V    |

| Note: Permanent device damage may occur in<br>should be restricted to the conditions as<br>maximum rating conditions for extended | s specified in the operation | nal sections of this data shee  |      |

# Table 6. Thermal Characteristics

| Parameter                              | Symbol | Test Condition | Value | Unit |

|----------------------------------------|--------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | ΦJA    | Still Air      | 35    | °C/W |

## **Functional Description**

The Si5540 is a fully integrated, low power, SONET/ SDH transmitter for OC-192/STM-64 applications. It combines a high performance clock multiplier unit (CMU) with a 16:1 serializer that has a low-speed interface compliant with the Optical Interface Forum (OIF) SFI-4 standard.

The CMU uses a phase-locked loop (PLL) architecture based on Silicon Laboratories' proprietary DSPLL<sup>™</sup> technology. This technology is used to generate ultralow jitter clock and data outputs that provide significant margin to the SONET/SDH specifications. The DSPLL architecture also utilizes a digitally implemented loop filter that eliminates the need for external loop filter components. As a result, sensitive noise coupling nodes that typically cause degraded jitter performance in crowded PCB environments are removed.

The DSPLL also reduces the complexity and performance requirements of reference clock distribution strategies for OC-192/STM-64 optical port cards. This is possible because the DSPLL provides selectable wideband and narrowband loop filter settings that allow the user to set the jitter attenuation characteristics of the CMU to accommodate reference clock sources that have a high jitter content. Unlike traditional analog PLL implementations, the loop filter bandwidth is controlled by a digital filter inside the DSPLL and can be changed without any modification to external components.

#### DSPLL<sup>™</sup> Clock Multiplier Unit

The Si5540's clock multiplier unit (CMU) uses Silicon Laboratories' proprietary DSPLL technology to generate a low jitter, high frequency clock source capable of producing a high speed serial clock and data output with significant margin to the SONET/SDH specifications. This is achieved by using a digital signal processing (DSP) algorithm to replace the loop filter commonly found in analog PLL designs. This algorithm processes the phase detector error term and generates a digital control value to adjust the frequency of the voltage controlled oscillator (VCO). Because external loop filter components are not required, sensitive noise entry points are eliminated, thus making the DSPLL less susceptible to board-level noise sources. Therefore, SONET/SDH jitter compliance is easier to attain in the application.

#### Programmable Loop Filter Bandwidth

The digital loop filter in the Si5530 provides two bandwidth settings that support either wideband or narrowband jitter transfer characteristics. The filter bandwidth is selected via the BWSEL control input. In traditional PLL implementations, changing the loop filter bandwidth would require changing the values of external loop filter components.

In narrowband mode, a loop filter cutoff of 12 kHz is provided. This setting makes the Si5540 more tolerant of jitter on the reference clock source. As a result, the complexity of the clock distribution circuitry used to generate the physical layer reference clocks can be simplified without compromising jitter margin to the SONET/SDH specification.

In wideband mode, the loop filter provides a cutoff of 50 kHz. This setting is desirable in applications where the reference clock is provided by a low jitter source like the Si5364 Clock Synchronization IC or Si5320 Precision Clock Multiplier/Jitter Attenuator IC. This allows the DSPLL to more closely track the precision reference source resulting in the best possible jitter performance.

#### **Reference Clock**

The CMU within the Si5530 is designed to operate with reference clock sources that are either 1/16th or 1/64th the desired output data rate. The CMU will support operation with data rates between 9.9 Gbps and 10.7 Gbps and the reference clock should be scaled accordingly. For example, to support 10.66 Gbps operation the reference clock source would be approximately 167 MHz or 666 MHz. The REFRATE input pin is used to configure the device for operation with one of the two supported reference clock submultiples of the data rate.

The Si5540 supports operation with two selectable reference clock sources. The first configuration uses an externally provided reference clock that is input via REFCLK. The second configuration uses the parallel data clock, TXCLK16IN, as the reference clock source. When using TXCLK16IN as the reference source, the narrowband loop filter setting may be preferable to remove jitter that may be present on the data clock. The selection of reference clock configuration is controlled via the REFSEL input. The Si5540 will drive the TXLOL output high to indicate the DSPLL has locked to the selected reference source.

#### Serialization

The Si5540 includes serialization circuitry that combines a FIFO with a parallel to serial shift register. Low speed data on the parallel input bus, TXDIN[15:0], is latched into the FIFO on the rising edge of TXCLK16IN. The data in the FIFO is clocked into the

shift register by an output clock, TXCLK16OUT, that is produced by dividing down the high speed transmit clock, TXCLKOUT, by a factor of 16. The TXCLK16OUT clock output is provided to support 16 bit word transfers between the Si5540 and upstream devices using a counter clocking scheme. The high-speed serial data stream is clocked out of the shift register using TXCLKOUT.

#### Input FIFO

The Si5540 integrates a FIFO to decouple data transferred into the FIFO via TXCLK16IN from data transferred into the shift register via TXCLK16OUT. The FIFO is eight parallel words deep and accommodates any static phase delay that may be introduced between TXCLK16OUT and TXCLK16IN in counter clocking schemes. Further, the FIFO will accommodate a phase drift or wander between TXCLK16IN and TXCLK16OUT of up to three parallel data words.

The FIFO circuitry indicates an overflow or underflow condition by asserting FIFOERR high. This output can be used to recenter the FIFO read/write pointers by tieing it directly to the FIFORST input. The Si5540 will also recenter the read/write pointers after the device's power on reset, external reset via RESET, and each time the DSPLL transitions from an out of lock state to a locked state (TXLOL transitions from low to high).

#### Parallel Input To Serial Output Relationship

The Si5540 provides the capability to select the order in which data on the parallel input bus is transmitted serially. Data on this bus can be transmitted MSB first or LSB first depending on the setting of TXMSBSEL. If TXMSBSEL is tied low, TXDIN0 is transmitted first followed in order by TXDIN1 through TXDIN15. If TXMSB-SEL is tied high, TXDIN15 is transmitted first followed in order by TXDIN14 through TXDIN0. This feature simplifies board routing when ICs are mounted on both sides of the PCB.

#### **Transmit Data Squelch**

To prevent the transmission of corrupted data into the network, the Si5540 provides a control pin that can be used to force the high speed data output, TXDOUT, to 0. By driving TXSQLCH low TXDOUT will be forced to 0.

#### Reset

A device reset can be forced by holding the RESET pin low for at least 1  $\mu$ s. When RESET is asserted low, the input FIFO pointers reset and the digital control circuitry initializes. When RESET transitions high to start normal operation, the DSPLL will be calibrated.

#### **Clock Disable**

The Si5540 provides a clock disable pin, TXCLKDSBL, that is used to disable the high-speed serial data clock output, TXCLKOUT. When the TXCLKDSBL pin is asserted, the positive and negative terminals of CLK-OUT are tied to 1.5 V through 50  $\Omega$  on-chip resistors. This feature is used to reduce power consumption in applications that do not use the high speed transmit data clock.

#### **Bias Generation Circuitry**

The Si5540 makes use of an external resistor to set internal bias currents. The external resistor allows precise generation of bias currents which significantly reduces power consumption versus traditional implementations that use an internal resistor. The bias generation circuitry requires a  $3.09 \text{ k}\Omega$  (1%) resistor connected between REXT and GND.

#### **Differential Output Circuitry**

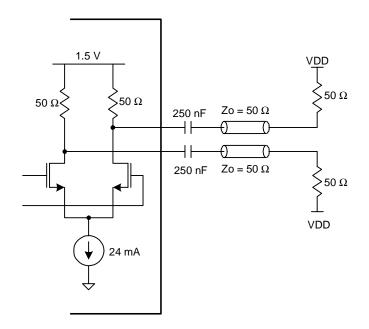

The Si5540 utilizes a current-mode logic (CML) architecture to drive the high speed serial output clock and data on TXCLKOUT and TXDOUT. An example of output termination with ac coupling is shown in Figure 4. In applications where direct dc coupling is possible, the 250 nF capacitors may be omitted. The differential peak-to-peak voltage swing of the CML architecture is listed in Table 2 on page 5.

Figure 4. CML Output Driver Termination (TXCLKOUT, TXDOUT)

## Si5540 Pinout: 99 BGA

| 10       | 9              | 8          | 7          | 6              | 5              | 4               | 3               | 2              | 1         | - |

|----------|----------------|------------|------------|----------------|----------------|-----------------|-----------------|----------------|-----------|---|

| TXDIN[12 | ?]- TXDIN[12]+ | TXDIN[14]- | TXDIN[14]+ | REFCLK-        | REFCLK+        | TXSQLCH         | RSVD_<br>VDD33  | REFRATE        |           | A |

| TXDIN[10 | )]+ TXDIN[11]+ | TXDIN[13]- | TXDIN[13]+ | TXDIN[15]-     | TXDIN[15]+     | TXCLKDSBL       | REFSEL          | RSVD_<br>VDD33 | GND       | в |

|          | )- TXDIN[11]-  | GND        | GND        | GND            | GND            | RESET           | VDD33           | GND            | TXCLKOUT+ | с |

| TXDIN[8] | I+ TXDIN[9]+   | GND        | VDD        | VDD            | VDD            | VDD             | RSVD_<br>GND    | GND            | TXCLKOUT- | D |

| TXDIN[8] | – TXDIN[9]–    | GND        | VDD        | VDD            | VDD            | VDD             | RSVD_<br>GND    | GND            | GND       | E |

| TXDIN[6  | + TXDIN[7]+    | GND        | VDD        | VDD            | VDD            | VDD             | RSVD_<br>GND    | GND            | TXDOUT+   | F |

| TXDIN[6] | – TXDIN[7]–    | GND        | VDD        | VDD            | VDD            | VDD             | RSVD_<br>GND    | GND            | TXDOUT-   | G |

| TXDIN[4  | ]+ TXDIN[5]+   | GND        | GND        | GND            | GND            | GND             | BWSEL           | NC             | GND       | н |

| TXDIN[4  | – TXDIN[5]–    | TXDIN[3]+  | TXDIN[3]-  | TXDIN[1]+      | TXDIN[1]-      | TXMSBSEL        | RSVD_<br>GND    | TXLOL          | REXT      | J |

| TXDIN[2] | + TXDIN[2]-    | TXDIN[0]+  | TXDIN[0]-  | TXCLK16<br>IN+ | TXCLK16<br>IN- | TXCLK16<br>OUT+ | TXCLK16<br>OUT- | FIFORST        | FIFOERR   | к |

|          |                |            |            |                |                |                 |                 |                |           | J |

Bottom View

Figure 5. Si5540 Pin Configuration (Bottom View)

| r | 1         | 2              | 3               | 4               | 5              | 6              | 7          | 8          | 9          | 10         |

|---|-----------|----------------|-----------------|-----------------|----------------|----------------|------------|------------|------------|------------|

| A |           | REFRATE        | RSVD_<br>VDD33  | TXSQLCH         | REFCLK+        | REFCLK-        | TXDIN[14]+ | TXDIN[14]- | TXDIN[12]+ | TXDIN[12]- |

| В | GND       | RSVD_<br>VDD33 | REFSEL          | TXCLKDSBL       | TXDIN[15]+     | TXDIN[15]-     | TXDIN[13]+ | TXDIN[13]- | TXDIN[11]+ | TXDIN[10]+ |

| с | TXCLKOUT+ | GND            | VDD33           | RESET           | GND            | GND            | GND        | GND        | TXDIN[11]- | TXDIN[10]- |

| D | TXCLKOUT- | GND            | RSVD_<br>GND    | VDD             | VDD            | VDD            | VDD        | GND        | TXDIN[9]+  | TXDIN[8]+  |

| E | GND       | GND            | RSVD_<br>GND    | VDD             | VDD            | VDD            | VDD        | GND        | TXDIN[9]-  | TXDIN[8]-  |

| F | TXDOUT+   | GND            | RSVD_<br>GND    | VDD             | VDD            | VDD            | VDD        | GND        | TXDIN[7]+  | TXDIN[6]+  |

| G | TXDOUT-   | GND            | RSVD_<br>GND    | VDD             | VDD            | VDD            | VDD        | GND        | TXDIN[7]-  | TXDIN[6]-  |

| н | GND       | NC             | BWSEL           | GND             | GND            | GND            | GND        | GND        | TXDIN[5]+  | TXDIN[4]+  |

| J | REXT      | TXLOL          | RSVD_<br>GND    | TXMSBSEL        | TXDIN[1]-      | TXDIN[1]+      | TXDIN[3]-  | TXDIN[3]+  | TXDIN[5]-  | TXDIN[4]-  |

| к | FIFOERR   | FIFORST        | TXCLK16<br>OUT- | TXCLK16<br>OUT+ | TXCLK16<br>IN- | TXCLK16<br>IN+ | TXDIN[0]-  | TXDIN[0]+  | TXDIN[2]-  | TXDIN[2]+  |

Top View

Figure 6. Si5540 Pin Configuration (Transparent Top View)

# Pin Descriptions: Si5540

| Pin Number(s)                                                      | Pin Name            | I/O | Signal Level | Description                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------|---------------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| НЗ                                                                 | BWSEL               | I   | LVTTL        | Bandwidth Select DSPLL.<br>This input selects loop bandwidth of the DSPLL.<br>BWSEL = 0: Loop bandwidth set to 12 kHz<br>BWSEL = 1: Loop bandwidth set to 50 kHz.                                                                                                                                                                                        |

| К1                                                                 | FIFOERR             | 0   | LVTTL        | <b>FIFO Error.</b><br>This output is driven high when a FIFO over-<br>flow/underflow has occurred. This output will<br>stick high until reset by asserting FIFORST.                                                                                                                                                                                      |

| К2                                                                 | FIFORST             | I   | LVTTL        | <b>FIFO Reset.</b><br>This input, when asserted high, resets the read/<br>write FIFO pointers to their initial state.                                                                                                                                                                                                                                    |

| B1, C5–8, C2, D8,<br>D2, E8, E1–2, F8,<br>F2, G8, G2, H4–<br>8, H1 | GND                 | GND |              | GND.                                                                                                                                                                                                                                                                                                                                                     |

| H2                                                                 | NC                  |     |              | No Connect.<br>Reserved for device testing; leave electrically<br>unconnected.                                                                                                                                                                                                                                                                           |

| A5–6                                                               | REFCLK+,<br>REFCLK– | I   | LVPECL       | <b>Differential Reference Clock.</b><br>The reference clock sets the operating fre-<br>quency of the PLL used to generate the output<br>clock frequency. The Si5540 will operate with<br>reference clock frequencies that are either 1/<br>16th or 1/64th the output clock rate.                                                                         |

| A2                                                                 | REFRATE             | I   | LVTTL        | <b>Reference Frequency Select.</b><br>This input configures the CMU to operate with<br>one of two possible reference clock frequen-<br>cies. When REFRATE = 1, the CMU will oper-<br>ate with a reference that is 1/16th the output<br>clock rate. When REFRATE = 0, the CMU will<br>operate with a reference that is 1/64th the out-<br>put clock rate. |

| B3                                                                 | REFSEL              | I   | LVTTL        | <b>Reference Clock Selection.</b><br>This inputs selects the reference clock source<br>used by the CMU. When REFSEL = 0, the low<br>speed data input clock, TXCLK16IN, is used as<br>the CMU reference. When REFSEL = 1, the ref-<br>erence clock provided on REFCLK is used.                                                                            |

| C4                                                                 | RESET               | I   | LVTTL        | Device Reset.<br>Forcing this input low for at least 1 $\mu$ s will cause<br>a device reset. For normal operation, this pin<br>should be held high.                                                                                                                                                                                                      |

| Pin Number(s)                                                                    | Pin Name                      | I/O | Signal Level | Description                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------|-------------------------------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1                                                                               | REXT                          |     |              | <b>External Bias Resistor.</b><br>This resistor is used by onboard circuitry to<br>establish bias currents within the device. This<br>pin must be connected to GND through a                                                                                             |

| D3, E3, F3, G3,<br>J3                                                            | RSVD_GND                      | _   |              | 3.09 kΩ (1%) resistor.Reserved Tie to Ground.Must tie directly to GND for proper operation.                                                                                                                                                                              |

| A3, B2                                                                           | RSVD_VDD33                    | _   |              | Reserved Tie to VDD33.<br>Must tie directly to VDD33 for proper operation.                                                                                                                                                                                               |

| K5–6                                                                             | TXCLK16IN–,<br>TXCLK16IN+     | I   | LVDS         | <b>Differential Data Clock Input.</b><br>The rising edge of this input clocks data present<br>on TXDIN into the device.                                                                                                                                                  |

| K3–4                                                                             | TXCLK16OUT+,<br>TXCLK16OUT–   | 0   | LVDS         | <b>Divided Down Output Clock.</b><br>This clock output is generated by dividing down<br>the high speed output clock, TXCLKOUT, by a<br>factor of 16. It is intended for use in counter<br>clocking schemes that transfer data between<br>the system ASIC and the Si5540. |

| Β4                                                                               | TXCLKDSBL                     | I   | LVTTL        | High Speed Clock Disable.<br>When this input is high, the output driver for<br>TXCLKOUT is disabled. In applications that do<br>not require the output data clock, the output<br>clock driver should be disabled to save power.                                          |

| C1, D1                                                                           | TXCLKOUT+,<br>TXCLKOUT-       | 0   | CML          | High Speed Clock Output.<br>The high speed output clock, TXCLKOUT, is<br>generated by the PLL in the clock multiplier<br>unit. It's frequency is nominally 16 or 64 times<br>the selected reference source.                                                              |

| A7–10, B5–10,<br>C9–10, D9–10,<br>E9–10, F9–10,<br>G9–10, H9–10,<br>J5–10, K7–10 | TXDIN[15:0]–,<br>TXDIN[15:0]+ | I   | LVDS         | <b>Differential Parallel Data Input.</b><br>The 16-bit data word present on these pins is<br>multiplexed into a high speed serial stream and<br>output on TXDOUT. The data on these inputs is<br>clocked into the device by the rising edge of<br>TXCLKIN.               |

| F1, G1                                                                           | TXDOUT+,<br>TXDOUT–           | 0   | CML          | <b>Differential High Speed Data Output.</b><br>The 16-bit word input on TXDIN[15:0] is multiplexed into a high speed serial stream that is output on these pins. This output is updated by the rising edge of TXCLKOUT.                                                  |

| J2                                                                               | TXLOL                         | 0   | LVTTL        | <b>CMU Loss-of-Lock.</b><br>The output is asserted low when the CMU is not<br>phase locked to the selected reference source.                                                                                                                                             |

| Pin Number(s)              | Pin Name | I/O   | Signal Level   | Description                                                                                                                                                                                                                        |

|----------------------------|----------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J4                         | TXMSBSEL | I     | LVTTL          | Data Bus Transmit Order.<br>For TXMSBSEL = 0, data on TXDIN[0] is trans-<br>mitted first followed by TXDIN[1] through<br>TXDIN[15].<br>For TXMSBSEL = 1, TXDIN[15] is transmitted<br>first followed by TXDIN[14] through TXDIN[0]. |

| A4                         | TXSQLCH  | I     | LVTTL          | Transmit Data Squelch.If TXSQLCH is asserted low, the output datastream on TXDOUT will be forced to 0. IfTXSQLCH = 1, TX squelching is turned off.                                                                                 |

| D4–7, E4–7,<br>F4–7, G4–7, | VDD      | VDD   | 1.8 V          | Supply Voltage.<br>Nominally 1.8 V.                                                                                                                                                                                                |

| C3                         | VDD33    | VDD33 | 1.8 V or 3.3 V | <b>Digital Output Supply.</b><br>Must be tied to either 1.8 V or 3.3 V. When tied to 3.3 V, LVTTL compatible output voltage swings on TXLOL and FIFOERR are supported.                                                             |

# Ordering Guide

| Part Number | Package | Temperature   |  |

|-------------|---------|---------------|--|

| Si5540-BC   | 99 BGA  | –40°C to 85°C |  |

### Table 7. Ordering Guide

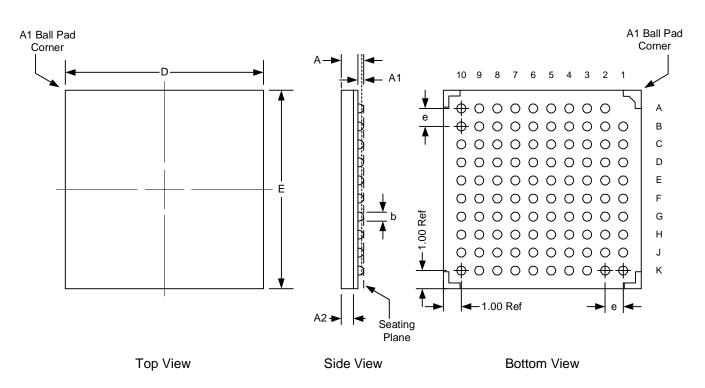

## **Package Outline**

Figure 7 illustrates the package details for the Si5540. Table 8 lists the values for the dimensions shown in the illustration.

Figure 7. 99-Ball Grid Array (BGA)

| Symbol | Millimeters |       |      |  |  |  |

|--------|-------------|-------|------|--|--|--|

|        | Min         | Nom   | Max  |  |  |  |

| A      | 1.30        | 1.40  | 1.50 |  |  |  |

| A1     | 0.31        | 0.36  | 0.41 |  |  |  |

| A2     | 0.65        | 0.70  | 0.75 |  |  |  |

| b      | —           | 0.46  | —    |  |  |  |

| D      | —           | 11.00 | —    |  |  |  |

| Е      | _           | 11.00 | —    |  |  |  |

| е      |             | 1.00  |      |  |  |  |

#### Table 8. Package Diagram Dimensions

# NOTES:

## **Contact Information**

#### Silicon Laboratories Inc.

4635 Boston Lane Austin, TX 78735 Tel: 1+(512) 416-8500 Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Email: productinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories, Silicon Labs, SiPHY, and DSPLL are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.